If we allow a single tap, we get to $b(n)=2n$. Here is an illustration with $n=8$: time elapses from left to right, the MVSFR shifts down, the next bit enters on top, the three taps are marked with *. The state is all-zeroes, except for the next bit that will drop out of the MVFSR. The taps are the next three bits that will drop out of the MVFSR.

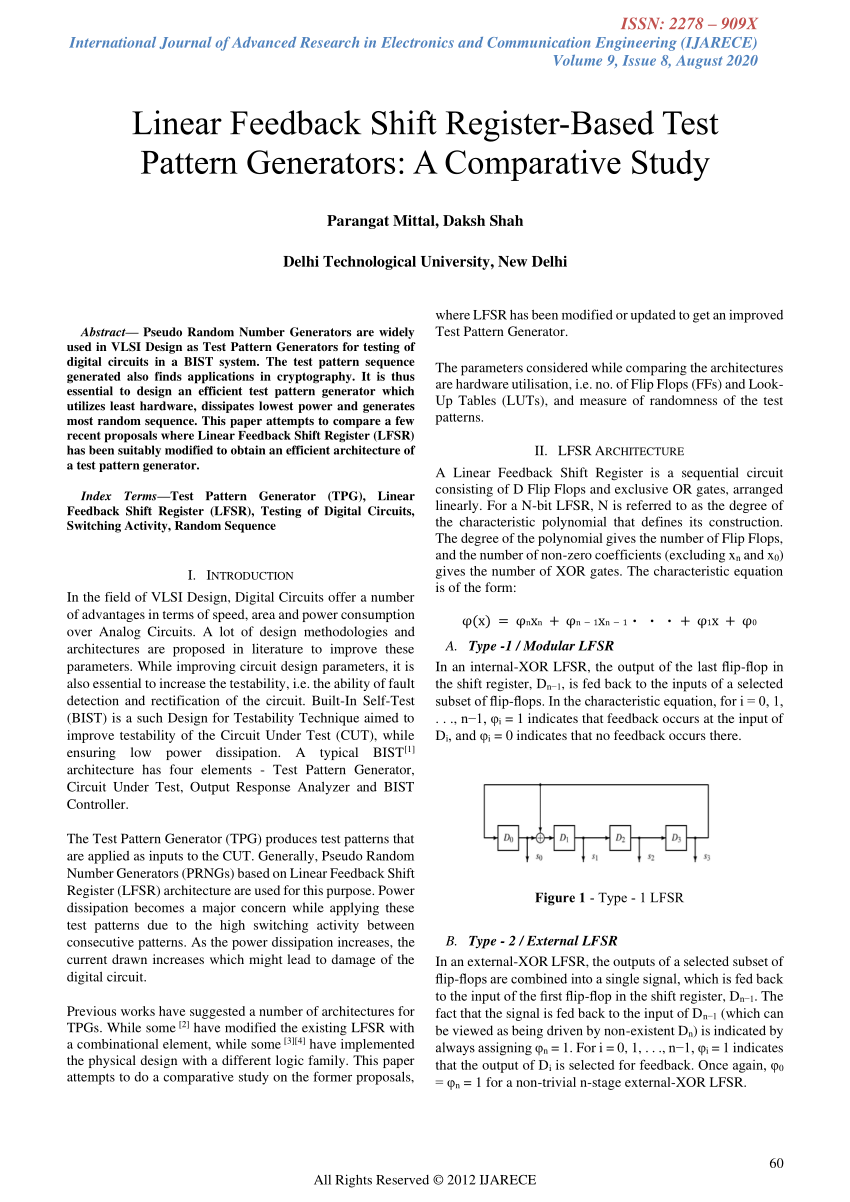

I have a construction with $b(n)=2n-2$ for $n\ge3$. Theory IT-30 (4): 587–594, 1984.I'm reading the question as asking for $b(n)$, the largest possible, such that we can exhibit distinct tap points (in odd number), and $n$-bit state, leading to a periodic sequence of (shortest) period at least $b(n)$ steps. Coppersmith, “Fast evaluation of logarithms in fields of characteristic two,” IEEE Trans. Built-in Test for VLSI, Wiley, New York, 1987, p. Dissertation, University of Manitoba, Winnipeg, Canada, 1987. Hortensius, “Parallel computation of non-deterministic algorithms in VLSI,” Ph.D. McCluskey, “A hybrid design of maximum-length sequence generators,” Proc. Chen, “Linear dependencies on linear feedback shift registers,” IEEE Trans. Dervisoglu, “VLSI self-testing using exhaustive bit patterns,” Tech. Cohn, “Design of universal test sequences for VLSI,” IEEE Trans. 13th Fault Tolerant Computing Symposium (FTCS-13), Milano, June 28–30, 1983, pp. Chen, “Logic test pattern generation using linear codes,” Proc.

Rosenberg, “Exhaustive generation of bit patterns with applications to VLSI self-testing,” IEEE Trans. Golomb, Shift Register Sequences, Holden Day, San Francisco, 1967. Savir, Built-in Test for VLSI, Wiley, New York, 1987, p.

McAnney, “Self-testing of multi-chip logic modules,” Digest of Papers, 1982 IEEE Test Conf., Philadelphia, November 15–18, pp. 1979 Test Conf., Cherry Hill, NJ, October, pp. Zwiehoff, “Built-in logic block observation techniques,” Proc.

0 kommentar(er)

0 kommentar(er)